- GENERATE A TEST BENCH WITH MODELSIM PE UPDATE

- GENERATE A TEST BENCH WITH MODELSIM PE CODE

- GENERATE A TEST BENCH WITH MODELSIM PE LICENSE

GENERATE A TEST BENCH WITH MODELSIM PE CODE

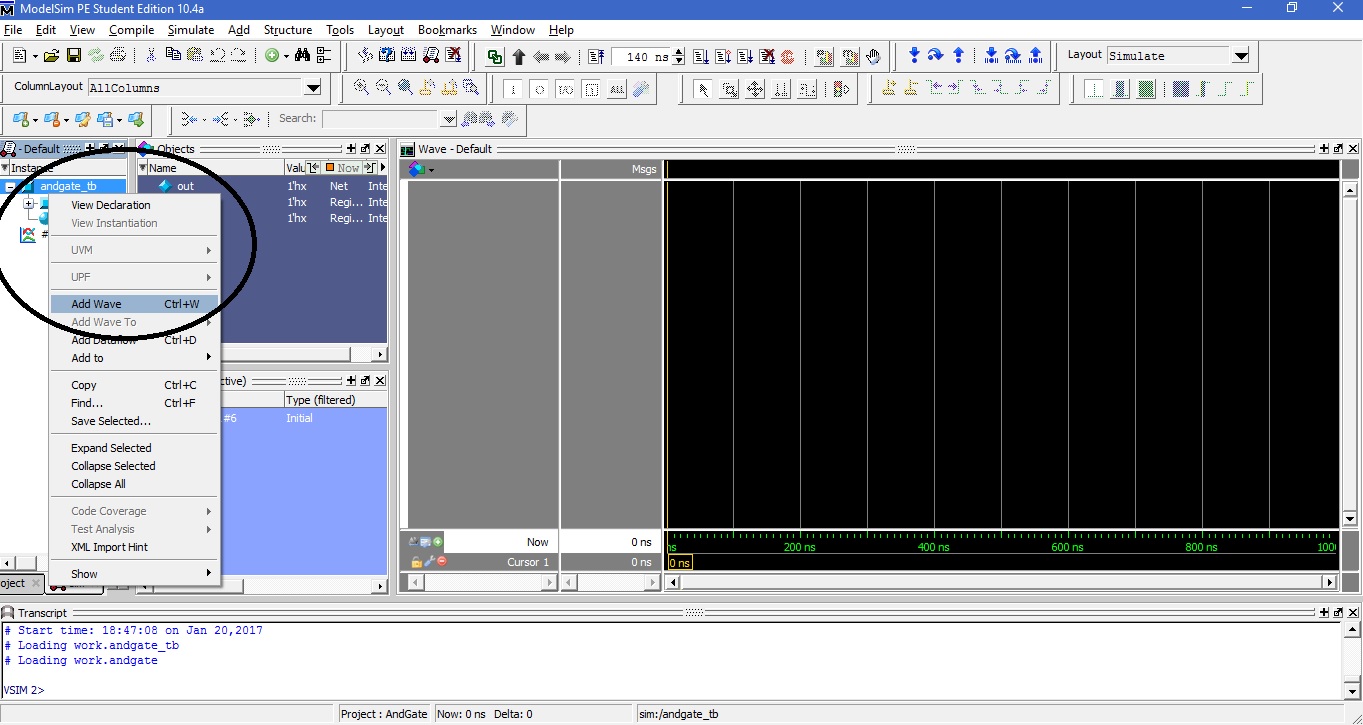

When using VHDL to design digital circuits, we normally also create a testbench to stimulate the code and ensure that the functionality is correct. Finally, we go through a complete test bench example. We then look at some key concepts such as the time type and time consuming constructs. We start by looking at the architecture of a VHDL test bench.

GENERATE A TEST BENCH WITH MODELSIM PE UPDATE

After each simulation, a short pause is added to ensure time for the HDL simulator to update the coverage result before the next iteration.In this post we look at how we use VHDL to write a basic testbench. After finishing each cosimulation session, there is no need to restart the HDL simulator since the HDL signal is reset properly at the beginning of each simulation. This example runs this model with all testcases to produce the code coverage result. There are nine testcases in the test bench model. ') ĭisp( 'HDL simulator is ready to cosimulate.') Nclaunch( 'tclstart',tclCmds, 'runmode', 'CLI', 'libfile', 'liblfihdls_gcc44.so') ĭisp( 'Waiting for HDL simulator to start. % Now we launch the HDL simulator and wait for it to be ready. % Load simulation 'puts "Ready for cosimulation."'. % Elaborate design with coverage enabled 'hdlsimulink -covoverwrite Controller'. % Compile VHDL code 'exec ncelab -64bit -coverage all -vhdl_time_precision 1ns -access +wc Controller'.

% Compile VHDL code 'exec ncvhdl -64bit -v93 cruise_hdlsrc/Controller.vhd'. 'exec ncvhdl -64bit -v93 cruise_hdlsrc/PI_Controller.vhd'. % Commands to compile and invoke Incisive with code coverage enabled. Then the HDL simulator advances its time by 40 ns to apply the reset, clock, and clk_enable signals before the cosimulation starts. When running each testcase, the "Pre-simulation Tcl commands" are applied in the HDL simulator first. This is to match the behavioral block, which updates its internal states right after the simulation starts.īased on the above considerations, the option "Time to run HDL simulator before cosimulation starts" is set to 40 ns.

We also want to run the HDL design past reset, but stop before the first active clock edge enabled by clk_enable. Therefore, the value of this parameter should be an integer multiple of the 10 ns clock period. The cosimulation starting time should be aligned with the falling edge of the HDL clock to avoid a race condition since the HDL signals change their values at the rising edge of the HDL clock. The reset signal is asserted from 0 to 27 ns. The clock enable signal is active at 37 ns.

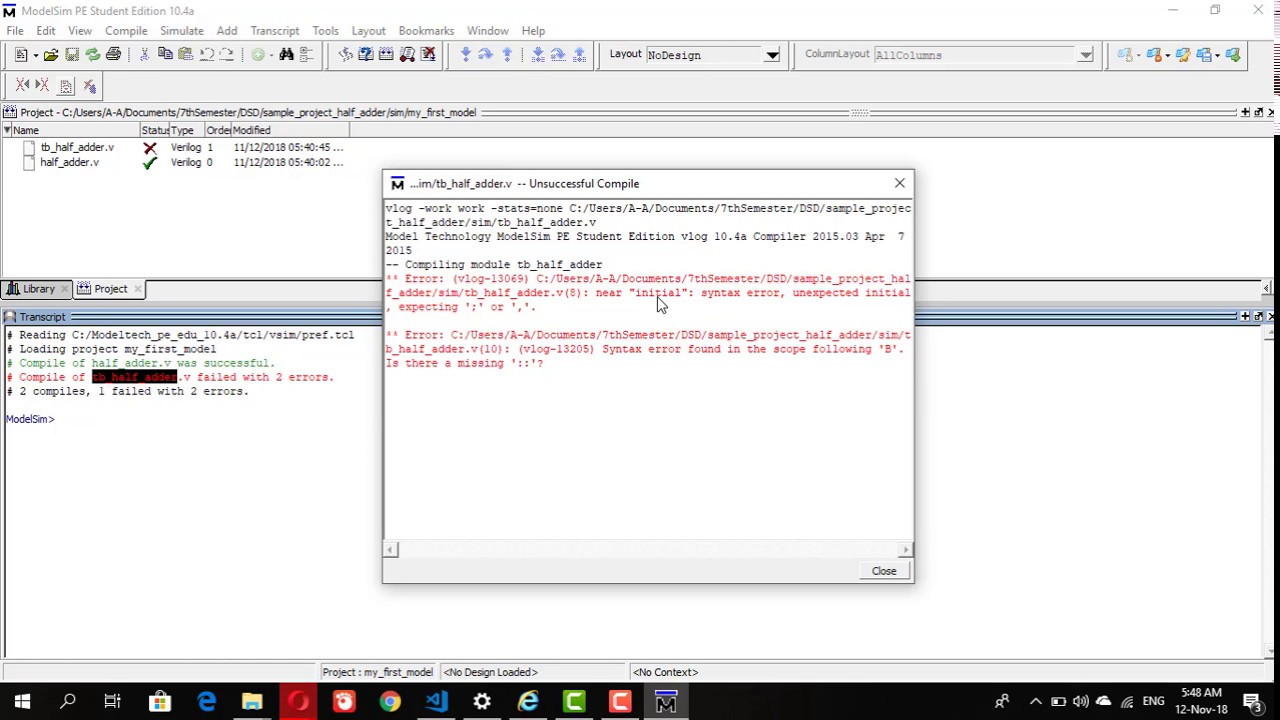

GENERATE A TEST BENCH WITH MODELSIM PE LICENSE

Make sure that your version of ModelSim has the proper code coverage license to run this example. Note that the code coverage function is an optional feature in ModelSim PE.

If you are using Incisive or Xcelium, close the ModelSim model and open the model cruise_control_incisive.slx. If you are using ModelSim or QuestaSim, the model cruise_control_modelsim.slx should be open. You do not need Simulink Design Verifier installed to run this example. This example shows that those automatically generated testcases also achieve complete HDL code coverage. The testcases in the test bench model are generated through Simulink Design Verifier™ from the original behavioral model for achieving complete model coverage. A test bench model is provided to verify the correctness of the HDL code by comparing the output of the HDL cosimulation block with that of the original behavioral block. The HDL code associated with this model is generated via HDL Coder™ from a Simulink behavioral model of the cruise controller.

0 kommentar(er)

0 kommentar(er)